Key Takeaway

Microsoft introduced the Maia 200, a custom AI inference chip designed to run large AI models faster and more efficiently, reduce power use and cost per inference, and materially lessen dependence on Nvidia GPUs while competing directly with Amazon and Google custom silicon.

Microsoft Launches Maia 200 Chip – Key Points

Maia 200 technical leap over Maia 100 (2023)

In January 2026, Microsoft announced the Maia 200, following the Maia 100 revealed at the Ignite conference in late 2023. The chip is built on TSMC’s 3nm process and contains over 140 billion transistors, optimized specifically for large-scale AI inference. Microsoft reports 10+ petaflops in 4-bit (FP4) precision and 5+ petaflops in 8-bit (FP8) performance, and describes native FP8/FP4 tensor cores as a core design choice for modern low-precision model serving. The chip is designed to operate within a 750W SoC TDP envelope, emphasizing datacenter-grade sustained inference rather than bursty benchmarks.

Inference optimization as a dominant cost driver

Inference (the process of serving trained models to users) has become one of the largest recurring costs for AI platforms. Unlike training, which is a one-time expense, inference scales linearly with usage. Microsoft frames Maia 200 as an accelerator engineered to improve the economics of AI token generation, aiming to lower ongoing inference costs, reduce power consumption, and lift throughput per deployed rack as AI services such as copilots and assistants reach massive daily request volume.

Capacity to run today’s largest models with future headroom

Microsoft stated that a single Maia 200 node can run today’s largest AI models with significant headroom for larger future models. This capability is intended to support successive generations of frontier models without requiring immediate redesigns of data center hardware, and to keep utilization high as model sizes and context windows expand.

Direct competition with hyperscaler chips

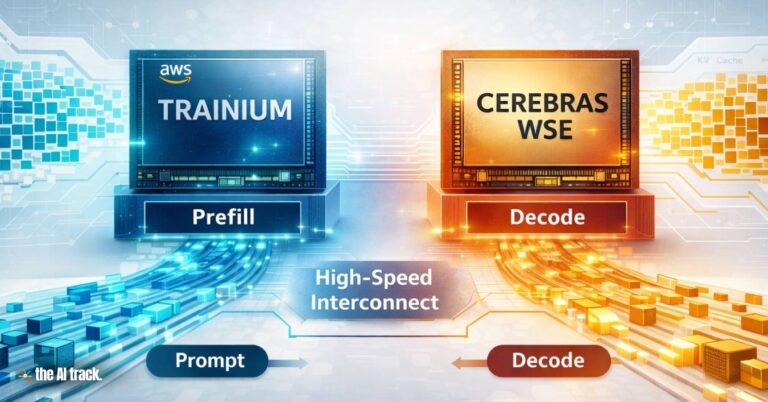

Microsoft explicitly benchmarked Maia 200 against rival custom silicon, claiming three times the FP4 performance of Amazon’s third-generation Trainium chips and FP8 performance above Google’s seventh-generation TPU on select benchmarks. Microsoft also positions Maia 200 as the most performant first-party silicon from a major cloud provider, reflecting a more aggressive comparative posture than the Maia 100 launch.

Performance-per-dollar gains

Microsoft reports that Maia 200 delivers approximately 30% better performance per dollar compared with the latest generation of hardware currently deployed across its data center fleet. The emphasis on performance-per-dollar is paired with system-level design choices intended to reduce total cost of ownership (TCO), including cluster-scale networking and integrated management within Azure.

Redesigned memory system and on-chip SRAM for busy inference

Maia 200 is presented as a “feed the model” design: a redesigned memory subsystem centered on narrow-precision datatypes, specialized data movement engines, and large local memory to prevent stalls during token generation. Microsoft specifies 216GB of HBM3e delivering 7 TB/s of bandwidth, plus 272MB of on-chip SRAM. This combination targets high-concurrency chatbot and assistant workloads where serving many simultaneous users can stress memory bandwidth and latency.

Reducing reliance on Nvidia GPUs

Like other cloud providers, Microsoft is pursuing vertically integrated silicon to reduce dependence on Nvidia GPUs, which remain central to AI infrastructure but carry high acquisition and operating costs. Maia allows Microsoft to offload a growing share of inference workloads from Nvidia hardware while retaining Nvidia GPUs where they remain optimal. Microsoft also pairs the chip strategy with software tooling intended to reduce lock-in effects created by Nvidia’s developer ecosystem.

Already deployed in production data centers

Maia 200 is not limited to lab testing. Microsoft confirmed that the chip is already running workloads in its US Central datacenter region near Des Moines, Iowa, with the US West 3 region near Phoenix, Arizona planned next, and additional regions expected to follow. Reporting also describes the Iowa deployment as coming online this week, indicating immediate operational rollout rather than a distant roadmap.

Powering flagship Microsoft and OpenAI models

Microsoft says Maia 200 is currently powering the latest GPT-5.2 models from OpenAI, Microsoft 365 Copilot, and internal projects from its Superintelligence team. The chip is also positioned as part of Microsoft’s broader AI platform stack supporting Microsoft Foundry, targeting improved performance per dollar for hosted model serving.

Tight hardware–software integration as a strategic advantage

Despite entering the custom AI chip race later than Google and Amazon, Microsoft argues that its advantage lies in tight integration between silicon, models, networking, and applications such as Copilot, treating the end-to-end inference system as one co-designed product. Microsoft also describes extensive pre-silicon validation that modeled LLM computation and communication patterns early, aiming to shorten the time from first silicon to production deployment.

Systems and networking designed for dense inference clusters

Maia 200 introduces a two-tier scale-up network design built on standard Ethernet, using a custom transport layer and tightly integrated NIC to avoid proprietary interconnect fabrics. Microsoft states each accelerator exposes 2.8 TB/s of bidirectional, dedicated scale-up bandwidth and supports predictable collective operations across clusters of up to 6,144 accelerators. Within each tray, four Maia accelerators are fully connected with direct, non-switched links, designed to keep high-bandwidth communication local and reduce network hops at scale.

Cooling, reliability, and datacenter-native management

Microsoft describes second-generation closed-loop liquid cooling using a Heat Exchanger Unit (HXU) and native integration with the Azure control plane for security, telemetry, diagnostics, and management at chip and rack levels. The company claims AI models were running on Maia 200 silicon within days of first packaged part arrival, and that time from first silicon to first datacenter rack deployment was reduced to less than half of comparable AI infrastructure programs.

Opening Maia 200 to external developers and researchers

Microsoft has announced a Maia 200 software development kit (SDK) and opened an early preview program for developers, academics, AI labs, and open-source model contributors. The toolchain is described as a full set of capabilities for model porting and optimization across heterogeneous accelerators, including PyTorch integration, a Triton compiler and optimized kernel library, access to a low-level programming language (NPL), plus a Maia simulator and cost calculator to optimize for efficiency earlier in the code lifecycle. Reporting also highlights Triton as an open-source tool with major contributions from OpenAI, positioned to address similar problem space to Nvidia’s CUDA tooling for developers.

Why This Matters

Custom inference chips like Maia 200 reflect a structural shift in AI economics. As AI products mature, inference – not training – becomes the dominant cost and performance bottleneck. Maia 200 strengthens Microsoft’s vertical integration across cloud infrastructure, AI models, and applications; increases competitive pressure on Nvidia in both hardware and developer tooling; and intensifies the arms race among hyperscalers to deliver cheaper, more energy-efficient AI at scale. The chip’s production deployment, explicit performance comparisons, and detailed system architecture (memory, networking, cooling, and SDK) indicate that custom silicon is moving from experimental to mission-critical infrastructure.

This article was drafted with the assistance of generative AI. All facts and details were reviewed and confirmed by an editor prior to publication.

Explore the vital role of AI chips in driving the AI revolution, from semiconductors to processors: key players, market dynamics, and future implications.

All you need to know about the critical components of AI infrastructure, hardware, software, and networking, that are essential for supporting AI workloads.

Microsoft announces a $3 billion investment in India to expand AI and cloud services, focusing on local talent and tech innovation.

Nvidia becomes first company to reach $5T market cap, driven by $500B chip orders, major deals with Intel, OpenAI, and Nokia, and record AI-fueled growth.

NVIDIA introduced the Rubin GPU within the Vera Rubin platform at CES 2026, targeting lower AI inference costs and expansion into physical AI systems.

Nvidia agreed in December 2025 to a $20 billion Groq deal that moves most staff and core AI inference assets to Nvidia while keeping Groq independent.

Read a comprehensive monthly roundup of the latest AI news!